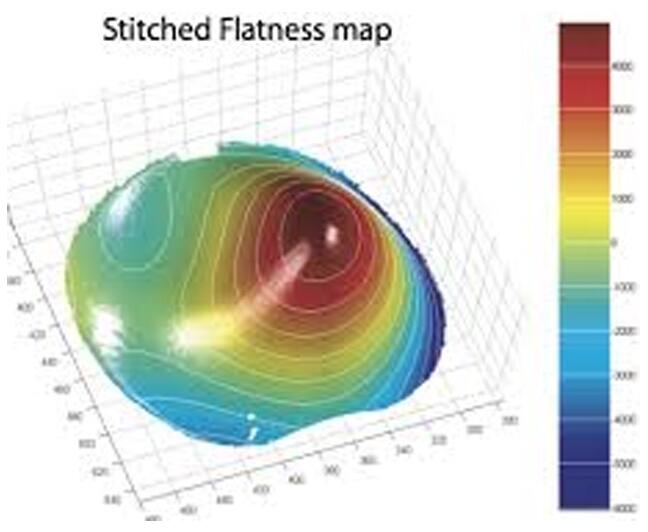

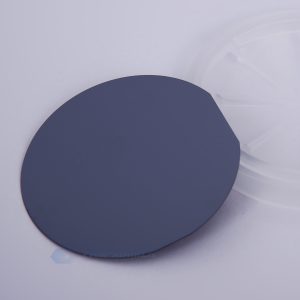

InAs Wafer

Compound semiconductor indium arsenide (InAs) wafer for sale is composed of indium and arsenic III-V elements grown by LEC (Liquid Encapsulated Czochralski). Ganwafer offers indium arsenide substrate in epi-ready or mechanical grade with n type, p type or semi-insulating in different orientations as terahertz radiation source.

Chất bán dẫn hợp chất arsenide indium là vật liệu bandgap trực tiếp, tương tự như gallium arsenide (GaAs). Đôi khi, InAs được sử dụng với InP. InAs được hợp kim hóa với GaAs tạo thành indium gallium arsenide. Thông số kỹ thuật khác của tấm wafer arsenide indium vui lòng xem như sau:

- Sự miêu tả

- Cuộc điều tra

Miêu tả

1. Thông số kỹ thuật của InAs Wafer

1.1. Đặc điểm kỹ thuật Wafer Indium Arsenide 4 inch

| Mục | Đặc tính kỹ thuật | |||

| dopant | pha tạp thấp | Stannum | Lưu huỳnh | Kẽm |

| Loại dẫn | N-type | N-type | N-type | P-type |

| wafer Đường kính | 4" | |||

| Định hướng Wafer | (100) ± 0,5 ° | |||

| Độ dày Wafer | 900 ± 25um | |||

| Tiểu Chiều dài phẳng | 16 ± 2mm | |||

| Chiều dài phẳng THCS | 8 ± 1mm | |||

| Carrier Nồng độ | 5 × 1016cm-3 | (5-20) x1017cm-3 | (1-10) x1017cm-3 | (1-10) x1017cm-3 |

| Mobility | ≥2 × 104cm2/ Vs | 7000-20000cm2/ Vs | 6000-20000cm2/ Vs | 100-400cm2/ Vs |

| EPD | <5 × 104cm-2 | <5 × 104cm-2 | <3 × 104cm-2 | <3 × 104cm-2 |

| TTV | <15um | |||

| CÂY CUNG | <15um | |||

| LÀM CONG | <20um | |||

| khắc laser | theo yêu cầu | |||

| Hoàn thiện bề mặt | P / E, P / P | |||

1.2. Đặc điểm kỹ thuật chất nền Arsenide Indium 3 inch

| Mục | Đặc tính kỹ thuật | |||

| dopant | pha tạp thấp | Stannum | Lưu huỳnh | Kẽm |

| Loại dẫn | N-type | N-type | N-type | P-type |

| wafer Đường kính | 3 " | |||

| Định hướng Wafer | (100) ± 0,5 ° | |||

| Độ dày Wafer | 600 ± 25um | |||

| Tiểu Chiều dài phẳng | 22 ± 2mm | |||

| Chiều dài phẳng THCS | 11 ± 1mm | |||

| Carrier Nồng độ | 5 × 1016cm-3 | (5-20) x1017cm-3 | (1-10) x1017cm-3 | (1-10) x1017cm-3 |

| Mobility | ≥2 × 104cm2/ Vs | 7000-20000cm2/ Vs | 6000-20000cm2/ Vs | 100-400cm2/ Vs |

| EPD | <5 × 104cm-2 | <5 × 104cm-2 | <3 × 104cm-2 | <3 × 104cm-2 |

| TTV | <12um | |||

| CÂY CUNG | <12um | |||

| LÀM CONG | <15um | |||

| khắc laser | theo yêu cầu | |||

| Hoàn thiện bề mặt | P / E, P / P | |||

| Epi sẵn sàng | Vâng | |||

| gói | Độc wafer container hoặc băng cassette | |||

| Epi sẵn sàng | Vâng | |||

| gói | Độc wafer container hoặc băng cassette | |||

1.3. Đặc điểm kỹ thuật Wafer InAs Wafer Compound Semiconductor 2 inch

| Mục | Đặc tính kỹ thuật | |||

| dopant | pha tạp thấp | Stannum | Lưu huỳnh | Kẽm |

| Loại dẫn | N-type | N-type | N-type | P-type |

| wafer Đường kính | 2 " | |||

| Định hướng Wafer | (100) ± 0,5 ° | |||

| Độ dày Wafer | 500 ± 25um | |||

| Tiểu Chiều dài phẳng | 16 ± 2mm | |||

| Chiều dài phẳng THCS | 8 ± 1mm | |||

| Carrier Nồng độ | 5 × 1016cm-3 | (5-20) x1017cm-3 | (1-10) x1017cm-3 | (1-10) x1017cm-3 |

| Mobility | ≥2 × 104cm2/ Vs | 7000-20000cm2/ Vs | 6000-20000cm2/ Vs | 100-400cm2/ Vs |

| EPD | <5 × 104cm-2 | <5 × 104cm-2 | <3 × 104cm-2 | <3 × 104cm-2 |

| TTV | <10um | |||

| CÂY CUNG | <10um | |||

| LÀM CONG | <12um | |||

| khắc laser | theo yêu cầu | |||

| Hoàn thiện bề mặt | P / E, P / P | |||

| Epi sẵn sàng | Vâng | |||

| gói | Độc wafer container hoặc băng cassette | |||

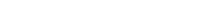

2. Bản đồ độ phẳng được khâu của InAs Wafer:

3. Ứng dụng của Arsenide Indium

Tinh thể arsenide Indi có độ linh động và tỷ lệ linh động điện tử cao (μe / μh = 70), hiệu ứng điện trở từ trường thấp và hệ số nhiệt độ nhỏ. Vì vậy, dung dịch arsenide indium là một lý tưởng để sản xuất thiết bị Hall và thiết bị điện trở từ.

Chất nền InAs đơn tinh thể có thể phát triển InAsSb / InAsPSb, InAsPSb và các vật liệu dị cấu trúc khác để sản xuất các thiết bị phát sáng hồng ngoại có bước sóng 2-12um.

Các chất nền đơn tinh thể của Indium Arsenides cũng có thể được sử dụng để phát triển trực tiếp các vật liệu cấu trúc siêu mạng InAsPSb để tạo ra các laser thác lượng tử trung hồng ngoại. Các thiết bị hồng ngoại này có triển vọng ứng dụng tốt trong lĩnh vực phát hiện khí và thông tin liên lạc bằng sợi quang suy hao thấp.

4. Ảnh hưởng của quá trình ủ đến các lớp tích lũy điện tử bề mặt của InAs Wafer

Sử dụng quang phổ Raman để khảo sát ảnh hưởng của nhiệt độ ủ đến tính chất quang học của lớp tích tụ electron bề mặt wafer indium arsenide n loại (100). Kết quả cho thấy các đỉnh Raman gây ra bởi các phonon LO không được sàng lọc sẽ biến mất khi nhiệt độ tăng. Chúng ta cũng có thể thấy rằng lớp tích tụ điện tử trên bề mặt arsenide indium được loại bỏ bằng cách ủ. Cơ chế phân tích bằng nhiễu xạ tia X, quang phổ quang điện tử tia X và kính hiển vi điện tử truyền qua độ phân giải cao cho thấy các pha In2O3 và As2O3 vô định hình được tích lũy trên đế wafer InAs trong quá trình ủ; một dạng tinh thể mỏng Là màng mỏng được hình thành ở mặt phân cách giữa lớp oxit và chất nền wafer, dẫn đến giảm độ dày lớp electron trên bề mặt.