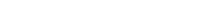

SiC Epi Wafer

O wafer epitaxial de SiC é um tipo de wafer de carboneto de silício em que um único filme de cristal (camada epitaxial) com certos requisitos e o mesmo cristal que o substrato é cultivado no substrato de SiC. Em aplicações práticas, quase todos os dispositivos semicondutores de banda larga são fabricados em pastilhas epitaxiais, enquanto a própria pastilha de carbeto de silício é usada apenas como substrato, incluindo o substrato para crescimento epitaxial de GaN.

- Descrição

- Investigação

Descrição

Em comparação com os dispositivos de energia tradicionais baseados em Si, os materiais de cristal único de SiC não podem fabricar diretamente o dispositivo de energia de SiC. O wafer de SiC epitaxy com alta qualidade deve ser cultivado em substrato condutor de SiC. Em seguida, use os wafers SiC epi para fabricar os dispositivos.

O epitaxial é um processo importante em todo o fluxo da indústria de semicondutores. Como os dispositivos são quase obtidos por crescimento epitaxial, a qualidade da pastilha epitaxial de carboneto de silício terá um grande efeito no desempenho dos dispositivos. Além disso, o epitaxial está na posição intermediária de todo o processo do semicondutor, que é muito afetado pelo processamento do cristal e do substrato. Em suma, o processo epitaxial desempenha um papel importante no desenvolvimento da indústria.

1. Especificação do Wafer Epitaxial SiC

1.1 Especificação do Wafer Epitaxial de Carbeto de Silício de 4”

| Itens | N-tipo | Típica | P-tipo | Típica |

| Especificação | Especificação | |||

| Diâmetro | 4" (100 mm) | - | 4" (100 mm) | - |

| Poly-type | 4H | - | 4H | - |

| Superfície | (0001) Face de silicone | - | (0001) Face de silicone | - |

| Desorientação para <11-20> | 4 graus desligado | - | 4 graus desligado | - |

| Condutividade | do tipo n | - | tipo p | - |

| dopante | Não dopado, Nitrogênio | - | Alumínio | - |

| Concentração transportadora | <1E14,2E14-2E19 cm-3 | - | 2E14-2E19 cm-3 | - |

| Tolerância | ±18% | ±14% | ±48% | ±24% |

| Uniformidade | < 14% | 8% | < 19% | 14% |

| Faixa de espessura | 0,5-100 μm | - | 0,5-30 μm | - |

| Tolerância | 8% | ±4% | ±8% | ±4% |

| Uniformidade | <5% | 1,80% | <5% | 1,80% |

1.2 Especificação de 6” SiC Epi Wafer

| Itens | N-tipo | Típica | P-tipo | Típica |

| Especificação | Especificação | |||

| Diâmetro | 6" (150 mm) | - | 6" (150 mm) | - |

| Poly-type | 4H | - | 4H | - |

| Superfície | (0001) Face de silicone | - | (0001) Face de silicone | - |

| Desorientação para <11-20> | 4 graus desligado | - | 4 graus desligado | - |

| Condutividade | do tipo n | - | tipo p | - |

| dopante | Não dopado, Nitrogênio | - | Alumínio | - |

| Concentração transportadora | <1E14,2E14-2E19 cm-3 | - | 2E14-2E19 cm-3 | - |

| Tolerância | ±18% | ±14% | ±48% | ±24% |

| Uniformidade | < 14% | 0.08 | < 19% | 0.14 |

| Faixa de espessura | 0,5-80 μm | - | 0,5-30 μm | - |

| Tolerância | 0.08 | ±4% | ±8% | ±4% |

| Uniformidade | <5% | 2% | <5% | 2% |

Nota:

* No mercado SiC epi wafer, todo o substrato SiC para crescimento de epi é grau de produção, e a exclusão de borda deve ser de 3mm;

* Camadas epi tipo N <20 mícrons são precedidas por camada tampão tipo n, E18 cm-3, 0,5 μm;

* Camadas epi tipo N≥20 mícrons são precedidas por camada tampão tipo n, E18, 1-5 μm;

* Nem todas as densidades de dopagem estão disponíveis em todas as espessuras;

* A dopagem do tipo N é determinada como um valor médio ao longo do wafer (17 pontos) usando Hg sonda CV;

* A espessura do wafer de SiC é determinada como um valor médio ao longo do wafer (9 pontos) usando FTIR;

* Uniformidade: desvio padrão (σ)/média.

2. Qual é a diferença entre SiC Epitaxy e Silicon Epitaxy?

O substrato SiC é geralmente cultivado por PVT com temperatura tão alta quanto 2000 ℃. No entanto, o ciclo de produção é longo; a saída é baixa. Comparado com o substrato de silício, o custo do substrato de SiC é muito alto.

Quanto ao processo epitaxial, o processo de epitaxia SiC é quase o mesmo que o do silício, mas haverá algumas diferenças no design da temperatura e no design da estrutura.

Devido à particularidade dos materiais, a tecnologia de processamento do dispositivo é diferente do silício. São adotados processos de alta temperatura, incluindo implantação de íons, oxidação e recozimento.

3. Quais são os parâmetros-chave do carboneto de silício Epi Wafer?

A espessura e a uniformidade da concentração de dopagem são os parâmetros mais básicos e fundamentais dos materiais epitaxiais de SiC. Na verdade, os parâmetros do SiC epi wafer dependem do design do dispositivo. Tome o seguinte caso como exemplo: diferentes níveis de tensão dos dispositivos determinarão os parâmetros epitaxiais. Especificamente, a espessura epitaxial do wafer de SiC deve ser de 6um a uma baixa tensão de 600V; a espessura do wafer de SiC deve ser de 10~15um em uma tensão média de 1200~1700V; a espessura das camadas epitaxiais de carboneto de silício deve ser superior a 100um a uma tensão >= 10000. A espessura epitaxial aumenta junto com o aumento da capacidade de tensão. É mais difícil cultivar wafers de SiC epi de alta qualidade, pois há um grande desafio no controle de defeitos, especialmente em aplicações de alta tensão.

De fato, o SiC epi tem muitos defeitos. Devido a diferentes cristais, seus defeitos também são diferentes. Os defeitos incluem principalmente microtúbulos, defeitos triangulares, defeitos superficiais de cenoura, agregação de escada e outros defeitos especiais. Vale a pena notar que muitos defeitos são diretamente do substrato. Portanto, a qualidade e o nível de processamento do substrato, principalmente o controle de defeitos, são muito importantes para o crescimento epitaxial.

Os defeitos epitaxiais do SiC são geralmente classificados em fatais e não fatais. Defeitos fatais, como defeitos triangulares e excrementos, têm impacto em todos os tipos de dispositivos, incluindo diodos, MOSFETs e dispositivos bipolares. O maior impacto é a tensão de ruptura, que pode reduzir a tensão de ruptura em 20% ou até 90%. Defeitos não fatais, como alguns TSD e TED, podem não afetar o diodo, e podem ter impacto na vida útil dos dispositivos MOS e bipolares, ou ter algum efeito de vazamento, o que acabará por afetar a taxa de qualificação de processamento de o dispositivo.

Os defeitos epitaxiais de carboneto de silício são geralmente divididos em defeitos fatais e defeitos não fatais. Defeitos fatais, como defeitos triangulares e gotejamento, podem afetar todos os tipos de dispositivos, como diodos, MOSFETs e dispositivos bipolares. A maior influência é a tensão de ruptura, caiu de 20%, até 90%. Defeitos não fatais, como alguns TSDs e Ted, podem não afetar os diodos, mas podem afetar a vida útil dos dispositivos MOS e bipolares, ou ter um certo efeito de vazamento. Eventualmente, isso afetará a taxa de qualificação de processamento do dispositivo.

A seguir estão várias sugestões para controlar defeitos epitaxiais da produção de wafer de SiC:

Em primeiro lugar, selecione cuidadosamente o material do substrato;

Em segundo lugar, selecione o equipamento e a localização;

Em terceiro lugar, escolha a tecnologia de processo adequada.

4. Qual o progresso da tecnologia epitaxial SiC?

No campo de média e baixa tensão, a espessura e a concentração de dopagem do wafer epitaxial de SiC podem ser relativamente boas. No entanto, no campo de alta tensão, ainda existem muitas dificuldades, incluindo espessura, uniformidade de concentração de dopagem, defeitos triangulares e assim por diante, a serem superadas.

Nas aplicações de média e baixa tensão, o processo de epitaxia SiC está maduro. O filme fino epitaxial de SiC pode atender às demandas de SBD, JBS, MOS e outros dispositivos em média e baixa tensão em geral. A espessura e concentração de dopagem de camadas epitaxiais de 10um em aplicações de dispositivos de 1200V são obtidas com um bom nível. Os defeitos de superfície podem atingir menos de 0,5 metros quadrados.

No campo de alta tensão, a tecnologia de epitaxia de carboneto de silício é relativamente atrasada. Um wafer epitaxial de SiC de 200um tem muita uniformidade, espessura e concentração para fabricar um dispositivo de 20.000 V. Enquanto isso, o filme espesso de SiC exigido por dispositivos de alta tensão tem muitos defeitos, especialmente os defeitos triangulares. Isso afetará a preparação dos dispositivos de alta corrente. Uma grande área de chip pode produzir uma grande corrente e a vida útil da portadora minoritária será baixa.

Em relação ao campo de alta tensão, os tipos de dispositivos tendem a usar dispositivos bipolares, exigindo maior vida útil da portadora minoritária. A vida útil do portador minoritário deve ser de pelo menos 5us ou mais para obter a corrente direta ideal. Os parâmetros de vida útil da portadora minoritária de wafers epitaxiais de SiC são 1~2us. Assim, isso não é tão importante para os dispositivos de alta tensão agora, mas precisa de tratamento técnico posterior.

5. Qual é a tecnologia de fabricação do SiC Epi Wafer?

A epitaxia de carbeto de silício possui duas tecnologias principais em equipamentos:

Modelo de crescimento de fluxo 1/passo proposto em 1980: Isso desempenha um papel muito importante no desenvolvimento e qualidade da epitaxia. Pode ser cultivada em temperatura relativamente baixa. Ao mesmo tempo, ele pode alcançar um controle muito estável para a forma de cristal 4H que estamos interessados em que o TCS seja introduzido para melhorar a taxa de crescimento.

2/A introdução do TCS pode atingir a taxa de crescimento mais de 10 vezes a taxa de crescimento tradicional. A introdução do TCS não só melhora a taxa de produção, mas também controla muito a qualidade, especialmente para o controle de gotas de silício. Portanto, é muito benéfico para o crescimento epitaxial de filme espesso. Esta tecnologia foi comercializada pela primeira vez pela LPE em 14 anos. Em cerca de 17 anos, a Aixtron atualizou o equipamento e transplantou a tecnologia para equipamentos comerciais.