SiCエピタキシャルウェーハの主要なパラメータは何ですか?

私たちが話している炭化ケイ素エピタキシャル成長のパラメータは、実際には主にデバイスの設計に依存します。 たとえば、デバイスの電圧グレードに応じて、SiCエピタキシャル成長のパラメータも異なります。

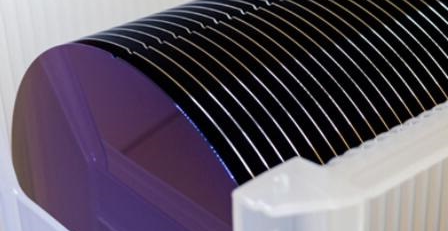

1.SiCエピタキシーの主要パラメーター

一般的に、600ボルトでの低圧、の厚さ炭化ケイ素エピタキシー約6μmで、1200〜1700の中圧で必要な厚さは10〜15μmです。 10,000ボルトを超える高電圧の場合、100μm以上が必要になる場合があります。 したがって、電圧容量の増加に伴い、炭化ケイ素エピタキシャル成長の厚さはそれに応じて増加します。 したがって、特に高電圧の分野では、高品質のエピタキシャルウェーハの準備は非常に困難です。 最も重要なことは欠陥制御であり、これは実際には非常に大きな課題です。

2.炭化ケイ素エピタキシャル成長の欠陥

炭化ケイ素エピタキシャル成長の欠陥は、一般に致命的な欠陥と非致死的な欠陥に分けられます。

三角形の欠陥や液滴などの致命的な欠陥は、ダイオード、MOSFET、バイポーラデバイスを含むすべてのデバイスタイプに影響を及ぼします。 デバイスへの最大の影響はブレークダウン電圧です。これにより、ブレークダウン電圧が20%低下するか、90%まで低下する可能性があります。

一部のTSDやTDのような非致死性の欠陥は、ダイオードに影響を与えない場合がありますが、MOS、バイポーラデバイス、またはリークの影響に寿命の影響を与える可能性があり、最終的にはデバイスの適格な処理速度に影響を与えます。

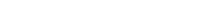

SiCエピタキシーの欠陥を制御するための最初の方法は、炭化ケイ素基板の材料を慎重に選択することです。 もう1つは機器の選択とローカリゼーションであり、3つ目はプロセス技術です。

3.炭化ケイ素エピタキシャル成長技術の進歩

低圧および中圧の分野では、コアパラメータの厚さとSiCエピタキシーのドーピング濃度を比較的優れたレベルで達成できます。

しかし、高圧の分野では、克服すべき多くの困難がまだあります。 主なパラメータ指標には、厚さ、ドーピング濃度の均一性、三角形の欠陥などが含まれます。

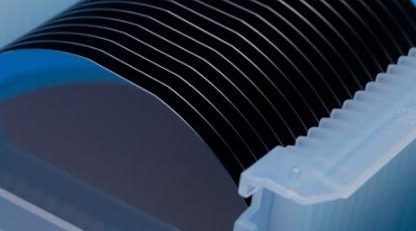

中電圧および低電圧アプリケーションの分野では、炭化ケイ素エピタキシャル成長技術は比較的成熟しており、基本的に低中電圧SBD、JBS、MOSおよびその他のデバイスのニーズを満たすことができます。 上記のように、10μmのエピタキシャルウェーハの1200ボルトのデバイスアプリケーションでは、その厚さとドーピング濃度は非常に優れたレベルに達し、表面欠陥も非常に良好で、0.5平方メートル下に達する可能性があります。

高電圧の分野でのエピタキシャル技術の開発は、比較的遅れています。 例えば、低圧での上記と比較した、200ボルトデバイス上の200μmの炭化ケイ素エピタキシャル材料の均一性、厚さ、および濃度は、特にドーピング濃度の均一性とはかなり異なる。

同時に、高電圧デバイスには厚膜が必要です。 ただし、まだ多くの欠陥、特に三角形の欠陥があります。SiCエピタキシャルウェーハ、主に大電流デバイスの準備に影響を与えます。 大電流は大きなチップ面積を必要とし、平均寿命は現在比較的短いです。

高電圧に関しては、デバイスのタイプはバイポーラデバイスになる傾向があり、マイノリティキャリアの寿命要件は比較的高くなります。 理想的な順方向電流を実現するには、少数キャリアの寿命が少なくとも5μs以上に達する必要がありますが、SiCエピタキシャルウェーハの現在の少数キャリアの寿命は約1〜2μsです。 そのため、高電圧デバイスの需要はまだ満たされておらず、炭化ケイ素ウェーハのエピタキシャル成長には、後処理技術が依然として必要です。

詳細については、メールでお問い合わせください。sales@ganwafer.comとtech@ganwafer.com.