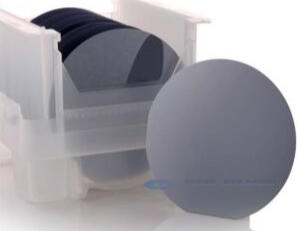

SiデルタドープGaAs PHEMTヘテロ構造

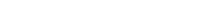

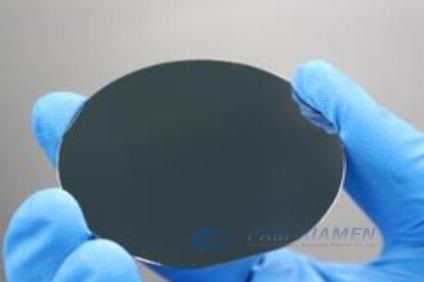

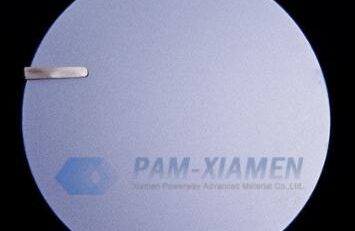

As a leading semiconductor wafer manufacturer, Ganwafer can supply III-V semiconductor epitaxial wafers, more specifications please refer to https://www.ganwafer.com/product/iii-v-epi-wafer/。 ここでは、デルタ ドープ GaAs pHEMT (疑似整合高電子移動度トランジスタ) ヘテロ構造を例に取り、ストップ層を備えたデルタ ドープ ヘテロ構造 DpHEMT の特定の層材料を以下の表に示します。 PHEMT は、最も広く使用されているマイクロ波およびミリ波パワー デバイスの 1 つです。 二重δドープGaAs pHEMT材料構造では、歪み層InGaAsチャネルの界面特性と成長品質が、材料の性能を決定する鍵となります。 ダブルデルタドーピングは、シングルデルタドーピングと比較して、GaAs pHEMTのキャリア濃度を効果的に増加させることがわかりました。

1. デルタドープ pHEMT ヘテロ構造

1.1 Epitaxial pHEMT Structure on GaAs Substrate

GANW201028-PHEMT

| レイヤー名 |

|

厚さ、ええと |

導電率タイプ |

|

|

| 接触層 | H17 | 0.080 | N | GaAsの | 5.0×1018 |

| 停止レイヤー | H16 | – | – | Al0.9Ga0.1As | – |

| バリア層 | H15 | – | – | Al0.22Ga0.78As | – |

| スペーサ層 | H14 | – | – | GaAsの | – |

| デルタ層 | H13 | – | – | シ | – |

| スペーサ層 | H12 | 0.0004 | – | GaAsの | – |

| スペーサ層 | H11 | – | – | Al0.23Ga0.77As | – |

| スペーサ層 | H10 | – | – | GaAsの | – |

| チャネル層 | H9 | – | – | In0.23Ga0.77As | |

| スペーサ層 | H8 | – | – | GaAsの | – |

| スペーサ層 | H7 | – | – | Al0.23Ga0.77As | – |

| スペーサ層 | H6 | – | – | GaAsの | – |

| デルタ層 | H5 | – | – | シ | 0.74×1012CM-2 |

| スペーサ層 | H4 | 0.0004 | – | GaAsの | – |

| バリア層 | H3 | – | – | Al0.23Ga0.77As | – |

| 緩衝ヘテロ構造 |

H2 |

– | – | GaAs、AlGaAs | – |

| substrate

(001) |

H1 |

625±25 | – | GaAsの | – |

1.2 Specification of Epitaxial РНЕМТ–1δ Structure on GaAs Substrate for Low Noise MMIC Applications

GANW190213-PHEMT

| レイヤー素材 | 厚さ | Doping (Concentration) | Notes |

| N+ GaAs | — | Si doped,(6E18 cm-3) | |

| n-Alバツジョージア1-xとして | — | Si doped, (–) | X=0.24±0.005 |

| i-Alバツジョージア1-xとして | 7 | アンドープ | X=0.24±0.005 |

| Delta- Si | — | Planar Si doped, (–) | |

| i-GaAs | — | アンドープ | |

| i-Alバツジョージア1-xとして | — | アンドープ | X=0.24±0.005 |

| i-GaAs | 1 | アンドープ | |

| でyジョージア1-yとして | — | アンドープ | — |

| GaAs (buffer 2) | — | アンドープ | |

| Superlattice | — | アンドープ | X=0.24±0.005 |

| アルバツジョージア1-xAs (3.2 nm)/ | |||

| GaAs (– nm), x 6 | |||

| GaAs (buffer 1) | 200 | アンドープ | |

| (100) GaAs substrate | アンドープ |

Remarks:

* layer thickness deviation less than 5%

* Doping referred to desirable channel electron concentration ns=1.7E12 cm-2 ±5 % (for the reference Hall structure with i-GaAs 4 nm cap layer rather than n+GaAs for transistor structure)

* Channel Hall mobility should exceed 7000 cm2/(V s) at room temperature (typical 7050-7150 cm2/(V s))

1.3 Specification of GaAs Epitaxial Р-НЕМТ 2δ Structure for Power Amplifier MMIC Applications

GANW190213-PHEMT

| レイヤー素材 | 厚さ | Doping (Concentration) | Notes |

| N+ GaAs | — | Si doped, (–) | |

| n-Alバツジョージア1-xとして | — | Si doped, 1E18 cm-3 | X=0.22±0.005 |

| Delta- Si | — | Planar Si doped, (–) | |

| n-Alバツジョージア1-xとして | 4 | Si doped, (–) | X=0.24±0.005 |

| i-Alバツジョージア1-xとして | — | アンドープ | X=0.24±0.005 |

| Delta- Si | — | Planar Si doped, (–) | |

| i-GaAs | 0.5 | アンドープ | |

| i-Alバツジョージア1-xとして | — | アンドープ | X=0.23±0.005 |

| i-GaAs | — | アンドープ | |

| でyジョージア1-yとして | 14 | アンドープ | – |

| i-GaAs | — | アンドープ | |

| i-Alバツジョージア1-xとして | — | アンドープ | X=0.23±0.005 |

| Delta- Si | — | Planar Si doped, (–) | |

| i-GaAs | 0.5 | アンドープ | |

| i-Alバツジョージア1-xとして | — | アンドープ | X=0.23±0.005 |

| GaAs (buffer 2) | — | アンドープ | |

| Superlattice | — | アンドープ | X=0.23 |

| アルバツジョージア1-xAs (– nm)/ | |||

| GaAs (– nm), x 6 | |||

| GaAs (buffer 1) | 150 | アンドープ | |

| (100) GaAs substrate | アンドープ |

Remarks:

* layer thickness deviation less than 5%

* Doping referred to desirable channel electron concentration ns=2.8E12 cm-2 ±10 % (for the reference Hall structure with i-GaAs 4 nm cap layer rather than n+GaAs for transistor structure)

* Channel Hall mobility should exceed 6100 cm2/(V s) at room temperature (typical 6200-6500 cm2/(V s))

2. Additional FAQ about Device Parameters on GaAs PHEMT Structure

Q: We need the following parameters for basic transistors:

Structure 1.2: Gm=630 mS/mm, Vth=-0.4 V, Ids0~300 mA/mm, Idsmax~ 550 mA/mm (Usd~2V) for Lg~0.15 um.

Structure 1.3: Gm=430 mS/mm, Vth=-1.2 V, Ids0~400 mA/mm, Idsmax~ 550 mA/mm (Usd~5V), Ubd~ 20 V, for Lg~0.25 um

So can your GaAs pHEMT structure meet these requirements?

A: Yes, we can understand and epitaxial these pHEMT structures to meet your requirement.

You want to match Gm, Idmax, Idss and Vth in addition to channel Hall mobility and channel electronic concentration requirements, it needs to adjust 2-3 Runs in order to finally meet your needs. This requires to make three structural fine-tuning for each structure before ordering 100 pieces, mainly to fine-tune the size of Idss, i.e. 12 pieces each time (6 pieces for each structure, one structure for each two pieces), do 2-3 times, which is expected to meet your needs, after your confirmation, you can place another 100 pieces of orders.

3. AlGaAs Spacer Layer and InGaAs Channel in GaAs PHEMT

AlGaAs サッパー層の存在により、ドナー不純物のイオン化が可能になり、イオン化されたドナーと電子が空間的に分離されます。 そしてドナーは障壁層側に留まり、電子はチャネル層に入る。 スペーサー層の存在により、イオン化ドナーと電子の間の距離が長くなり、両者間のクーロン散乱が減少するだけでなく、電子のイオン化不純物散乱がさらに減少し、電子の移動度と飽和速度が向上します。 . しかし、スペーサ層が厚くなると、電子がチャネル層に進入しにくくなり、スペーサ層が厚すぎると二次元電子ガスの濃度に影響を与え、pHEMTデバイスの性能が低下します。 .

インジウム ガリウム ヒ素 (InGaAs) 材料のバンド ギャップは、ガリウム ヒ素 (GaAs) およびアルミニウム ガリウム ヒ素 (AlGaAs) のバンド ギャップよりも狭いため、ワイド バンド ギャップ材料と組み合わせることによって形成されるヘテロ接合は、より大きな伝導帯の不連続性を持ち、その量子ポテンシャル井戸は二次元に非常に敏感です。電子ガスの閉じ込め効果がより強くなり、より高い二次元電子ガス濃度とより大きなキャリア移動度が得られます。 GaAs pHEMT データシートは、AlGaAs/GaAs 材料と比較して、InGaAs/GaAs 材料は格子定数の差が大きいため、ミスマッチの程度が大きく、InGaAs チャネル層の成長厚さを制御することで低減できることを示しています。

4. Delta Doping of PHEMT Technology

プレーナドーピング技術によりトラップ効果が弱められ、ピンチオフ電圧が十分に制御され、ゲートの耐圧が向上し、チャネルのキャリア濃度が増加します。 平面ドーピング技術の利点を考慮して、平面ドーピング技術(すなわち、デルタドーピング技術)もGaAs pHEMTトランジスタに使用される。

GaAs pHEMT プロセスのデルタ ドーピングには、単一平面ドーピングと二重平面ドーピングの 2 種類があります。 チャネル層とスペーサ層を成長させた後、チャネル層上部にドナー不純物シリコンを数原子層だけ成長させた後、AlGaAsバリア層を再度成長させます。 このドーピング方法は、単一面ドーピングです。 二重面ドーピングとは、2 つのヘテロ接合を持つ pHEMT で、シリコン原子層が、ドーピングのために InGaAs チャネル層の両側の順方向接合と逆方向接合の両方で成長することです。

単一面ドープpHEMTでは、チャネルの上部にドープされたヘテロ接合が1つしかなく、接合界面に形成される三角形のポテンシャル井戸に2次元電子ガスが存在します。 デュアルプレーン ドープ pHEMT チャネル層の上部と下部の両方のヘテロ接合がドープされ、2 つのドープされた三角形のポテンシャル井戸は、ポテンシャル井戸の幅が比較的小さいため、ほぼ正方形のポテンシャル井戸を形成します。 もともと、2 つのドープされた三角形のポテンシャルは 2 次元電子ガスを持っているため、pHEMT の 2 次元電子ガスの濃度は高く、正方形のポテンシャル井戸が形成されているため、2 次元電子ガスに対する制限効果はより明白です。 、従って、GaAsに基づくpHEMTの性能は、より良好な線形性、より高い利得帯域幅など、改善される。

詳細については、メールでお問い合わせください。 sales@ganwafer.com と tech@ganwafer.com.