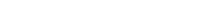

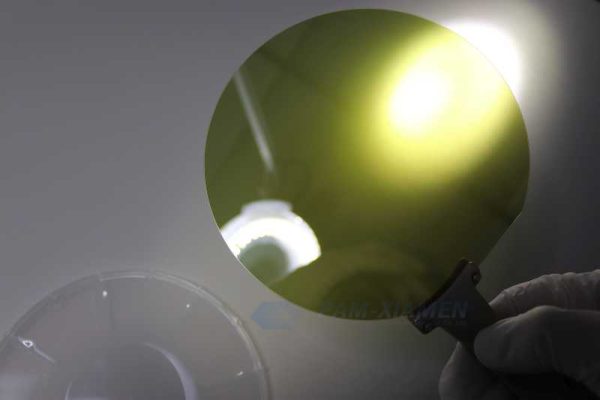

SiC Epi Wafer

Il wafer epitassiale SiC è un tipo di wafer di carburo di silicio in cui un film di cristallo singolo (strato epitassiale) con determinati requisiti e lo stesso cristallo del substrato viene fatto crescere sul substrato di SiC. Nelle applicazioni pratiche, quasi tutti i dispositivi semiconduttori a banda larga sono fabbricati su wafer epitassiali, mentre lo stesso wafer di carburo di silicio viene utilizzato solo come substrato, incluso il substrato per la crescita epitassiale del GaN.

- Descrizione

- Inchiesta

Descrizione

Rispetto ai tradizionali dispositivi di alimentazione a base di Si, i materiali a cristallo singolo SiC non possono fabbricare direttamente il dispositivo di alimentazione SiC. Il wafer di epitassia SiC di alta qualità deve essere coltivato su substrato conduttivo di SiC. Quindi, utilizzare i wafer SiC epi per fabbricare i dispositivi.

L'epitassile è un processo importante nell'intero flusso dell'industria dei semiconduttori. Poiché i dispositivi sono quasi ottenuti mediante crescita epitassiale, la qualità del wafer epitassiale di carburo di silicio avrà un grande effetto sulle prestazioni dei dispositivi. Inoltre, l'epitassile si trova nella posizione centrale dell'intero processo a semiconduttore, che è fortemente influenzato dall'elaborazione del cristallo e del substrato. Tutto sommato, il processo epitassiale gioca un ruolo importante nello sviluppo del settore.

1. Specifiche del wafer epitassiale SiC

1.1 Specifiche del wafer epitassiale al carburo di silicio da 4 pollici

| Elementi | Tipo N | Tipico | Di tipo P | Tipico |

| Specificazione | Specificazione | |||

| Diametro | 4 "(100 mm) | — | 4 "(100 mm) | — |

| Poly-type | 4H | — | 4H | — |

| Superficie | (0001) Faccia di silicone | — | (0001) Faccia di silicone | — |

| Fuori orientamento verso <11-20> | 4 gradi di spegnimento | — | 4 gradi di spegnimento | — |

| Conduttività | tipo n | — | tipo p | — |

| drogante | Non drogato, azoto | — | Alluminio | — |

| Concentrazione Carrier | <1E14,2E14-2E19 cm-3 | — | 2E14-2E19 cm-3 | — |

| Tolleranza | ±18% | ±14% | ±48% | ±24% |

| Uniformità | < 14% | 8% | < 19% | 14% |

| Gamma di spessori | 0,5-100 micron | — | 0,5-30 micron | — |

| Tolleranza | 8% | ±4% | ±8% | ±4% |

| Uniformità | < 5% | 1,80% | < 5% | 1,80% |

1.2 Specifiche del wafer SiC Epi da 6 pollici

| Elementi | Tipo N | Tipico | Di tipo P | Tipico |

| Specificazione | Specificazione | |||

| Diametro | 6 "(150 mm) | — | 6 "(150 mm) | — |

| Poly-type | 4H | — | 4H | — |

| Superficie | (0001) Faccia di silicone | — | (0001) Faccia di silicone | — |

| Fuori orientamento verso <11-20> | 4 gradi di spegnimento | — | 4 gradi di spegnimento | — |

| Conduttività | tipo n | — | tipo p | — |

| drogante | Non drogato, azoto | — | Alluminio | — |

| Concentrazione Carrier | <1E14,2E14-2E19 cm-3 | — | 2E14-2E19 cm-3 | — |

| Tolleranza | ±18% | ±14% | ±48% | ±24% |

| Uniformità | < 14% | 0.08 | < 19% | 0.14 |

| Gamma di spessori | 0,5-80 micron | — | 0,5-30 micron | — |

| Tolleranza | 0.08 | ±4% | ±8% | ±4% |

| Uniformità | < 5% | 2% | < 5% | 2% |

Nota:

* Nel mercato dei wafer SiC epi, tutto il substrato SiC per la crescita epi è di grado produttivo e l'esclusione del bordo dovrebbe essere di 3 mm;

* Gli strati epi di tipo N <20 micron sono preceduti da uno strato tampone di tipo n, E18 cm-3, 0,5 μm;

* Gli strati epi di tipo N≥20 micron sono preceduti da uno strato tampone di tipo n, E18, 1-5 μm;

* Non tutte le densità di drogaggio sono disponibili in tutti gli spessori;

* Il drogaggio di tipo N è determinato come valore medio attraverso il wafer (17 punti) utilizzando la sonda Hg CV;

* Lo spessore del wafer SiC è determinato come valore medio attraverso il wafer (9 punti) utilizzando FTIR;

* Uniformità: deviazione standard (σ)/media.

2. Qual è la differenza tra l'epitassia di SiC e l'epitassia di silicio?

Il substrato SiC viene solitamente coltivato da PVT con una temperatura fino a 2000 ℃. Tuttavia, il ciclo produttivo è lungo; l'uscita è bassa. Rispetto al substrato di silicio, il costo del substrato di SiC è molto elevato.

Per quanto riguarda il processo epitassiale, il processo epitassiale SiC è quasi lo stesso del silicio, ma ci saranno alcune differenze nel design della temperatura e nel design della struttura.

A causa della particolarità dei materiali, la tecnologia di elaborazione del dispositivo è diversa dal silicio. Vengono adottati processi ad alta temperatura tra cui l'impianto di ioni, l'ossidazione e la ricottura.

3. Quali sono i parametri chiave di Epi Wafer al carburo di silicio?

Lo spessore e l'uniformità della concentrazione di drogaggio sono i parametri più basilari e chiave dei materiali epitassiali SiC. In realtà, i parametri dell'epi wafer SiC dipendono dal design del dispositivo. Prendi il seguente caso come esempio: diversi livelli di tensione dei dispositivi determineranno i parametri epitassiali. Nello specifico, lo spessore epitassiale del wafer SiC dovrebbe essere 6um a una bassa tensione di 600V; lo spessore del wafer SiC dovrebbe essere 10~15um a una tensione media di 1200~1700V; lo spessore degli strati epitassiali di carburo di silicio dovrebbe essere superiore a 100 um a una tensione >= 10000. Lo spessore epitassiale aumenta insieme all'aumento della capacità di tensione. È più difficile coltivare wafer SiC epi di alta qualità poiché esiste una grande sfida nel controllo dei difetti, specialmente nelle applicazioni ad alta tensione.

In effetti, SiC epi ha molti difetti. A causa dei diversi cristalli, anche i loro difetti sono diversi. I difetti includono principalmente microtubuli, difetti triangolari, difetti superficiali della carota, aggregazione della scala e altri difetti speciali. Vale la pena notare che molti difetti provengono direttamente dal substrato. Pertanto, la qualità e il livello di lavorazione del substrato, in particolare il controllo dei difetti, sono molto importanti per la crescita epitassiale.

I difetti epitassiali SiC sono generalmente classificati in fatali e non fatali. Difetti fatali, come difetti triangolari ed escrementi, hanno un impatto su tutti i tipi di dispositivi, inclusi diodi, MOSFET e dispositivi bipolari. L'impatto maggiore è la tensione di rottura, che può ridurre la tensione di rottura del 20% o addirittura del 90%. Difetti non fatali, come alcuni TSD e TED, potrebbero non avere alcun effetto sul diodo e potrebbero avere un impatto sulla vita dei dispositivi MOS e bipolari, o avere qualche effetto di perdita, che alla fine influirà sul tasso di qualificazione dell'elaborazione di il dispositivo.

I difetti epitassiali del carburo di silicio sono generalmente suddivisi in difetti fatali e difetti non fatali. Difetti mortali come difetti triangolari e gocciolamento possono interessare tutti i tipi di dispositivi, come diodi, MOSFET e dispositivi bipolari. L'influenza maggiore è la tensione di rottura, scesa dal 20%, addirittura al 90%. Difetti non fatali, come alcuni TSD e Ted, potrebbero non influenzare i diodi, ma possono influire sulla durata dei dispositivi MOS e bipolari o avere un certo effetto di dispersione. Alla fine, influenzerà il tasso di qualificazione dell'elaborazione del dispositivo.

Di seguito sono riportati diversi suggerimenti per il controllo dei difetti epitassiali della produzione di wafer SiC:

In primo luogo, selezionare accuratamente il materiale del substrato;

In secondo luogo, seleziona l'attrezzatura e la localizzazione;

In terzo luogo, scegliere la tecnologia di processo adeguata.

4. Quali progressi della tecnologia epitassiale SiC?

Nel campo di media e bassa tensione, lo spessore e la concentrazione di drogaggio del wafer epitassiale SiC possono essere relativamente buoni. Tuttavia, nel campo dell'alta tensione, ci sono ancora molte difficoltà da superare, tra cui lo spessore, l'uniformità della concentrazione di drogante, i difetti triangolari e così via.

Nelle applicazioni a media e bassa tensione, il processo di epitassia SiC è maturo. Il film sottile epitassiale SiC può soddisfare le richieste di SBD, JBS, MOS e altri dispositivi a media e bassa tensione nel complesso. Lo spessore e la concentrazione di drogaggio di strati epitassiali di 10 um nelle applicazioni di dispositivi a 1200 V sono ottenuti con un buon livello. I difetti superficiali possono raggiungere meno di 0,5 mq.

Nel campo dell'alta tensione, la tecnologia dell'epitassia al carburo di silicio è relativamente arretrata. Un wafer epitassiale SiC da 200 um ha molta uniformità, spessore e concentrazione per la fabbricazione di un dispositivo da 20000 V. Nel frattempo, la spessa pellicola di SiC richiesta dai dispositivi ad alta tensione ha molti difetti, in particolare i difetti triangolari. Influirà sulla preparazione dei dispositivi ad alta corrente. Una grande area di chip può produrre una grande corrente e la durata del vettore di minoranza sarà bassa.

Per quanto riguarda il campo ad alta tensione, i tipi di dispositivi tendono a utilizzare dispositivi bipolari, richiedendo una maggiore durata dei portatori di minoranza. La durata della portante di minoranza deve essere di almeno 5 us o più per ottenere la corrente diretta ideale. I parametri di durata dei portatori minoritari dei wafer epitassiali SiC sono 1~2us. Pertanto, questo non è così importante per i dispositivi ad alta tensione ora, ma necessita di un successivo trattamento tecnico.

5. Qual è la tecnologia di fabbricazione di SiC Epi Wafer?

L'epitassia del carburo di silicio ha due principali tecnologie nelle apparecchiature:

Modello di crescita del flusso 1/Step proposto nel 1980: questo gioca un ruolo molto importante nello sviluppo e nella qualità dell'epitassia. Può essere coltivato a temperature relativamente basse. Allo stesso tempo, può ottenere un controllo molto stabile per la forma cristallina 4H a cui siamo interessati viene introdotto il TCS per migliorare il tasso di crescita.

2/L'introduzione del TCS può raggiungere il tasso di crescita più di 10 volte il tasso di crescita tradizionale. L'introduzione del TCS non solo migliora la velocità di produzione, ma controlla anche notevolmente la qualità, in particolare per il controllo delle goccioline di silicio. Pertanto, è molto vantaggioso per la crescita epitassiale di film spesso. Questa tecnologia è stata commercializzata per la prima volta da LPE in 14 anni. In circa 17 anni, Aixtron ha aggiornato le apparecchiature e trapiantato la tecnologia in apparecchiature commerciali.