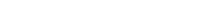

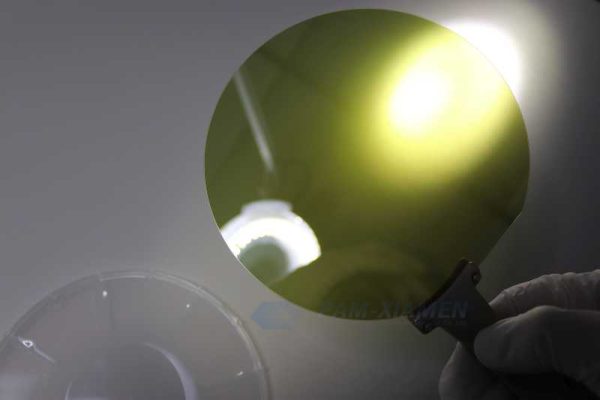

SiC-Epi-Wafer

SiC-Epitaxiewafer ist eine Art Siliziumkarbidwafer, bei dem ein Einkristallfilm (Epitaxieschicht) mit bestimmten Anforderungen und dem gleichen Kristall wie das Substrat auf dem SiC-Substrat gezüchtet wird. In praktischen Anwendungen werden fast alle Halbleiterbauelemente mit breiter Bandlücke auf Epitaxialwafern hergestellt, während Siliziumkarbidwafer selbst nur als Substrat verwendet werden, einschließlich des Substrats für das epitaxiale GaN-Wachstum.

- Beschreibung

- Anfrage

Beschreibung

Verglichen mit herkömmlichen Si-basierten Leistungsbauelementen können SiC-Einkristallmaterialien das SiC-Leistungsbauelement nicht direkt herstellen. SiC-Epitaxiewafer mit hoher Qualität müssen auf leitfähigem SiC-Substrat gezüchtet werden. Verwenden Sie dann die SiC-Epi-Wafer, um die Geräte herzustellen.

Epitaxie ist ein wichtiger Prozessablauf in der gesamten Halbleiterindustrie. Da Bauelemente fast durch epitaxiales Wachstum erhalten werden, hat die Qualität des Siliziumkarbid-Epitaxiewafers einen großen Einfluss auf die Leistung der Bauelemente. Darüber hinaus befindet sich die Epitaxie in der mittleren Position des gesamten Halbleiterprozesses, der stark von der Kristall- und Substratbearbeitung beeinflusst wird. Alles in allem spielt der Epitaxieprozess eine wichtige Rolle bei der Entwicklung der Branche.

1. Spezifikation des SiC-Epitaxialwafers

1.1 Spezifikation des 4-Zoll-Siliziumkarbid-Epitaxialwafers

| Angebote | N-Typ | Typisch | P-Typ | Typisch |

| Spezifikation | Spezifikation | |||

| Durchmesser | 4″ (100 mm) | - - | 4″ (100 mm) | - - |

| Poly-Typ | 4H | - - | 4H | - - |

| Oberfläche | (0001) Silikon-Fläche | - - | (0001) Silikon-Fläche | - - |

| Off-Orientierung in Richtung <11-20> | 4 Grad aus | - - | 4 Grad aus | - - |

| Leitfähigkeit | n-Typ | - - | p-Typ | - - |

| Dotierstoff | Undotiert, Stickstoff | - - | Aluminium | - - |

| Ladungsträgerkonzentration | <1E14,2E14-2E19 cm-3 | - - | 2E14-2E19 cm-3 | - - |

| Toleranz | ±18% | ±14 % | ±48% | ±24% |

| Gleichmäßigkeit | < 14 % | 8% | < 19 % | 14% |

| Dickenbereich | 0,5–100 μm | - - | 0,5–30 μm | - - |

| Toleranz | 8% | ±4% | ±8% | ±4% |

| Gleichmäßigkeit | < 5 % | 1,80 % | < 5 % | 1,80 % |

1.2 Spezifikation des 6-Zoll-SiC-Epi-Wafers

| Angebote | N-Typ | Typisch | P-Typ | Typisch |

| Spezifikation | Spezifikation | |||

| Durchmesser | 6″ (150 mm) | - - | 6″ (150 mm) | - - |

| Poly-Typ | 4H | - - | 4H | - - |

| Oberfläche | (0001) Silikon-Fläche | - - | (0001) Silikon-Fläche | - - |

| Off-Orientierung in Richtung <11-20> | 4 Grad aus | - - | 4 Grad aus | - - |

| Leitfähigkeit | n-Typ | - - | p-Typ | - - |

| Dotierstoff | Undotiert, Stickstoff | - - | Aluminium | - - |

| Ladungsträgerkonzentration | <1E14,2E14-2E19 cm-3 | - - | 2E14-2E19 cm-3 | - - |

| Toleranz | ±18% | ±14 % | ±48% | ±24% |

| Gleichmäßigkeit | < 14 % | 0.08 | < 19 % | 0.14 |

| Dickenbereich | 0,5–80 μm | - - | 0,5–30 μm | - - |

| Toleranz | 0.08 | ±4% | ±8% | ±4% |

| Gleichmäßigkeit | < 5 % | 2% | < 5 % | 2% |

Hinweis:

* Auf dem SiC-Epi-Wafermarkt ist das gesamte SiC-Substrat für das Epi-Wachstum produktionstauglich, und der Randausschluss sollte 3 mm betragen;

* Epi-Schichten vom N-Typ < 20 Mikron gehen eine Pufferschicht vom N-Typ, E18 cm-3, 0,5 μm voraus;

* Epi-Schichten vom N-Typ ≥20 Mikron gehen eine Pufferschicht vom N-Typ, E18, 1–5 μm voraus;

* Nicht alle Dotierungsdichten sind in allen Dicken erhältlich;

* Dotierung vom N-Typ wird als Durchschnittswert über den Wafer (17 Punkte) unter Verwendung von Hg-Sonden-CV bestimmt;

* SiC-Waferdicke wird als Mittelwert über den Wafer (9 Punkte) mittels FTIR bestimmt;

* Einheitlichkeit: Standardabweichung (σ)/Durchschnitt.

2. Was ist der Unterschied zwischen SiC-Epitaxie und Silizium-Epitaxie?

Das SiC-Substrat wird normalerweise durch PVT bei einer Temperatur von bis zu 2000 ℃ gezüchtet. Der Produktionszyklus ist jedoch lang; der Ausgang ist niedrig. Verglichen mit Siliziumsubstrat sind die Kosten für SiC-Substrate sehr hoch.

Was den Epitaxieprozess betrifft, ist der SiC-Epitaxieprozess fast derselbe wie bei Silizium, aber es wird ein wenig Unterschiede im Temperaturdesign und im Strukturdesign geben.

Aufgrund der Besonderheit der Materialien unterscheidet sich die Geräteverarbeitungstechnologie von Silizium. Es werden Hochtemperaturprozesse einschließlich Ionenimplantation, Oxidation und Tempern angewendet.

3. Was sind die Schlüsselparameter von Siliziumkarbid-Epi-Wafern?

Dicke und Gleichmäßigkeit der Dotierungskonzentration sind die grundlegendsten und wichtigsten Parameter von SiC-Epitaxiematerialien. Tatsächlich hängen die Parameter des SiC-Epi-Wafers vom Gerätedesign ab. Nehmen wir als Beispiel den folgenden Fall: Unterschiedliche Spannungspegel der Geräte bestimmen die Epitaxieparameter. Insbesondere sollte die epitaxiale Dicke des SiC-Wafers 6 um bei einer niedrigen Spannung von 600 V betragen; die Dicke des SiC-Wafers sollte 10 bis 15 um bei einer mittleren Spannung von 1200 bis 1700 V betragen; Die Dicke von Siliziumkarbid-Epitaxieschichten sollte mehr als 100 um bei einer Spannung >= 10000 betragen. Die Epitaxiedicke nimmt mit zunehmender Spannungsbelastbarkeit zu. Es ist schwieriger, qualitativ hochwertige SiC-Epi-Wafer zu züchten, da es eine große Herausforderung bei der Defektkontrolle gibt, insbesondere bei Hochspannungsanwendungen.

Tatsächlich hat SiC epi viele Defekte. Aufgrund unterschiedlicher Kristalle sind auch ihre Defekte unterschiedlich. Die Defekte umfassen hauptsächlich Mikrotubuli, dreieckige Defekte, Oberflächenkarottendefekte, Leiteraggregation und andere spezielle Defekte. Es ist erwähnenswert, dass viele Defekte direkt vom Substrat stammen. Daher sind die Qualität und das Verarbeitungsniveau des Substrats, insbesondere die Kontrolle von Defekten, für das epitaktische Wachstum sehr wichtig.

SiC-Epitaxiedefekte werden im Allgemeinen in tödliche und nicht-tödliche Defekte eingeteilt. Schwerwiegende Defekte wie Dreiecksdefekte und Ausscheidungen wirken sich auf alle Arten von Geräten aus, einschließlich Dioden, MOSFETs und bipolare Geräte. Der größte Einfluss ist die Durchbruchspannung, die die Durchbruchspannung um 20 % oder sogar 90 % reduzieren kann. Nicht schwerwiegende Defekte, wie z. B. einige TSD und TED, haben möglicherweise keine Auswirkungen auf die Diode und können sich auf die Lebensdauer von MOS- und Bipolargeräten auswirken oder einen gewissen Einfluss auf Leckagen haben, was sich letztendlich auf die Verarbeitungsqualifikationsrate auswirkt das Gerät.

Siliziumkarbid-Epitaxialdefekte werden im Allgemeinen in schwerwiegende Defekte und nicht schwerwiegende Defekte unterteilt. Schwerwiegende Defekte wie dreieckige Defekte und Tropfen können alle Arten von Geräten betreffen, wie Dioden, MOSFETs und bipolare Geräte. Der größte Einfluss ist die Durchbruchspannung, die von 20 % auf sogar 90 % abfällt. Nicht schwerwiegende Defekte, wie einige TSDs und Ted, beeinträchtigen die Dioden möglicherweise nicht, können jedoch die Lebensdauer von MOS- und Bipolargeräten beeinträchtigen oder einen bestimmten Leckeffekt haben. Schließlich wirkt sich dies auf die Geräteverarbeitungsqualifizierungsrate aus.

Im Folgenden finden Sie einige Vorschläge zur Kontrolle epitaktischer Defekte bei der Herstellung von SiC-Wafern:

Wählen Sie zunächst das Substratmaterial sorgfältig aus;

Wählen Sie zweitens die Ausrüstung und den Standort aus;

Drittens wählen Sie die richtige Prozesstechnologie.

4. Welche Fortschritte bei der SiC-Epitaxie-Technologie?

Im Mittel- und Niederspannungsbereich können die Dicke und Dotierungskonzentration von SiC-Epitaxiewafern relativ gut sein. Auf dem Hochspannungsgebiet sind jedoch noch viele Schwierigkeiten zu überwinden, darunter Dicke, Gleichmäßigkeit der Dotierungskonzentration, dreieckige Defekte und so weiter.

In Mittel- und Niederspannungsanwendungen ist der SiC-Epitaxieprozess ausgereift. SiC-Epitaxie-Dünnschicht kann die Anforderungen von SBD, JBS, MOS und anderen Geräten bei mittlerer und niedriger Spannung insgesamt erfüllen. Die Dicke und Dotierungskonzentration von 10 um-Epitaxieschichten in 1200-V-Geräteanwendungen werden mit einem guten Niveau erreicht. Die Oberflächendefekte können weniger als 0,5 Quadratmeter erreichen.

Im Hochspannungsbereich ist die Siliziumkarbid-Epitaxie-Technologie relativ rückständig. Ein 200-um-SiC-Epitaxiewafer weist eine große Gleichmäßigkeit, Dicke und Konzentration zur Herstellung eines 20000-V-Bauelements auf. Inzwischen hat der dicke SiC-Film, der für Hochspannungsvorrichtungen erforderlich ist, viele Defekte, insbesondere die dreieckigen Defekte. Dies wirkt sich auf die Vorbereitung der Hochstromgeräte aus. Eine große Chipfläche kann einen großen Strom erzeugen, und die Lebensdauer von Minoritätsträgern wird gering sein.

Hinsichtlich des Hochspannungsfeldes neigen Vorrichtungstypen dazu, bipolare Vorrichtungen zu verwenden, was eine höhere Minoritätsträgerlebensdauer erfordert. Die Minoritätsträgerlebensdauer muss mindestens 5 us oder länger betragen, um den idealen Durchlassstrom zu erhalten. Die Minoritätsträger-Lebensdauerparameter von SiC-Epitaxialwafern sind 1~2 us. Somit ist dies für Hochvoltgeräte jetzt nicht so wichtig, sondern bedarf einer nachfolgenden technischen Behandlung.

5. Was ist die Herstellungstechnologie von SiC-Epi-Wafern?

Die Siliziumkarbid-Epitaxie hat zwei Haupttechnologien in der Ausrüstung:

1980 vorgeschlagenes 1/Step-Flow-Wachstumsmodell: Dies spielt eine sehr wichtige Rolle bei der Entwicklung und Qualität der Epitaxie. Es kann bei relativ niedriger Temperatur gezüchtet werden. Gleichzeitig kann es eine sehr stabile Kontrolle für die 4H-Kristallform erreichen, an der wir interessiert sind. TCS wird eingeführt, um die Wachstumsrate zu verbessern.

2/Die Einführung von TCS kann eine Wachstumsrate von mehr als dem 10-fachen der traditionellen Wachstumsrate erreichen. Die Einführung von TCS verbessert nicht nur die Produktionsrate, sondern kontrolliert auch stark die Qualität, insbesondere für die Kontrolle von Siliziumtröpfchen. Daher ist es für das Dickschicht-Epitaxiewachstum sehr vorteilhaft. Diese Technologie wurde erstmals seit 14 Jahren von LPE kommerzialisiert. In etwa 17 Jahren rüstete Aixtron die Ausrüstung auf und übertrug die Technologie auf kommerzielle Ausrüstung.